电路应用|一文带您了解时钟芯片(RTC,Real Time Clock/Calendar)工作原理、用途、及经典应用(PCF8563/FH8563)

时钟芯片(RTC,Real Time Clock/Calendar)是利用相位锁定技术(PLL)来产生时钟信号,可以控制不同元件之间的时序,以保证正常的数字电路运行。而晶振是基于电学特性的无源元器件,利用晶体振荡的方式来产生稳定的振荡信号。

时钟芯片(RTC,Real Time Clock/Calendar)的工作原理主要分为以下几个步骤:

1. 常数频率偏差矫正

在时钟芯片的内部,第一步是常数频率偏差矫正,为了保证时钟电路的稳定性和精度,需要纠正芯片本身在设计及加工上产生的固定频率偏差。

2. 时钟信号输入

时钟芯片需要输入一个外部的时钟信号,这个信号可以是外部振荡器产生的信号,也可以是来自于GPS信号等其他源头产生的信号。通常情况下,时钟芯片会自动选择最好的、最符合性能要求的输入时钟信号,并进行自动调整。

3. 相位锁定环路(PFD和CP)操作

时钟芯片中的相位锁定环路(PFD和CP)是整个时钟芯片中最重要的部分。PFD的作用是将输入的时钟信号与芯片内部的本地振荡器输出信号进行比较,并产生相位误差信号,CP的作用是接收PFD输出的信号并反馈给本地时钟发生器,使得输出的信号与输入的信号同步。

4. 输出时钟信号

经过PFD和CP之后,时钟芯片内部的本地时钟发生器的信号就与输入的时钟信号在相位和频率上已经达到很好的同步,此时输出的时钟信号就相当精度和稳定性了。时钟芯片最终输出的产生的信号可以是符合电子设备的各种需要的,例如PCI标准的合适的信号,时钟芯片也可以输出倍频或者分频后的信号,以适应不同的应用场合。

RTC 芯片内部时钟电路原理

芯片内部时钟电路是一种用于提供芯片内部时钟信号的电路。它通常由一个振荡器、一个分频器和一个时钟控制器组成。

振荡器是一种电路,它可以产生一个固定频率的时钟信号。振荡器可以是晶体振荡器(XO)、外部振荡器或内部振荡器。

分频器是一种电路,它可以将振荡器产生的时钟信号除以一个固定的数字,从而产生一个更低的频率的时钟信号。

时钟控制器是一种电路,它可以控制芯片内部的时钟信号,并将其发送到芯片内部的各个部件。它可以控制时钟信号的频率、相位和持续时间,以及时钟信号的输出频率。

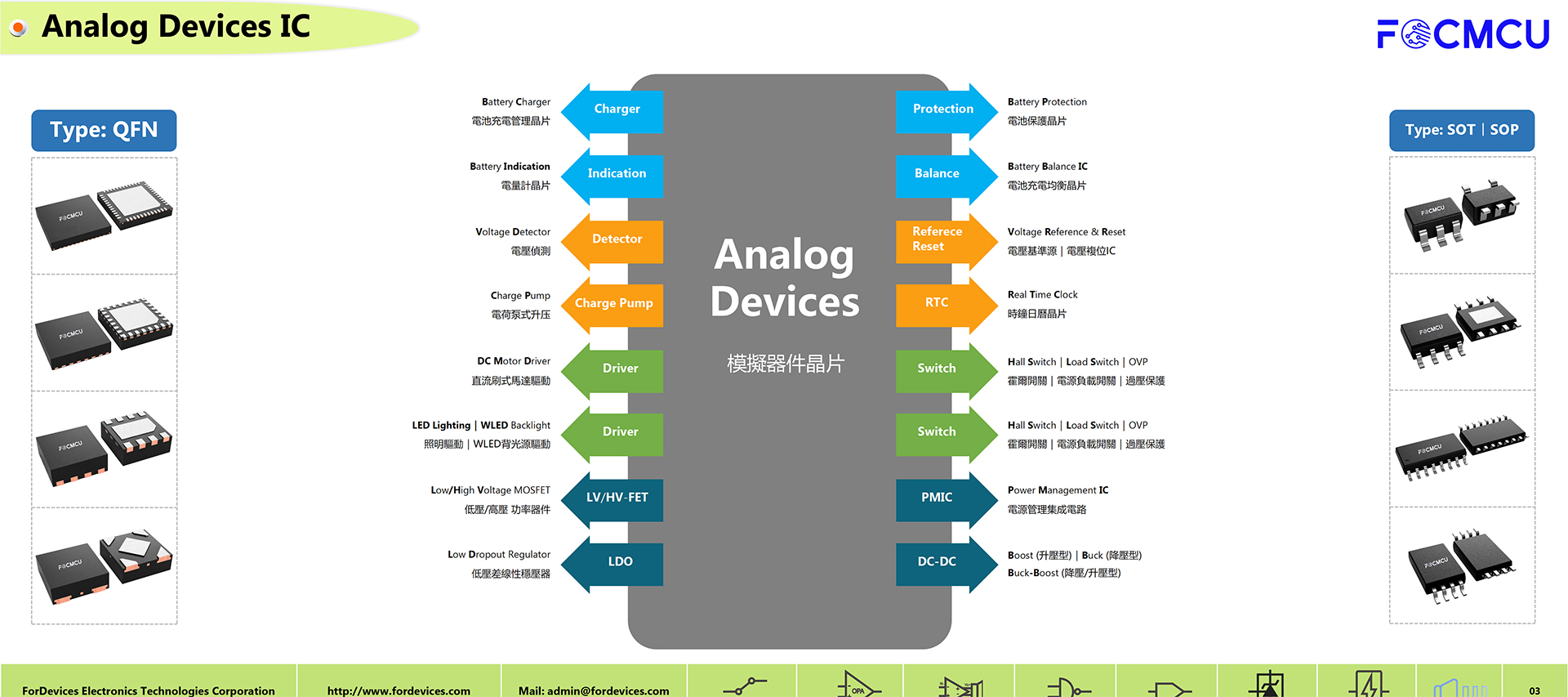

时钟芯片经典型号

PCF8563、FH8563、RX8025T、FM38025T、RX8010SJ、DS1302、DS1307

FH8563 器件介绍(带 I2C 接口的实时时钟/日历芯片)

FH8563 是一款低功耗CMOS实时时钟/日历芯片,它内置一个包括世纪、年、月、日、时、分、秒、星期的计时器,在电路中起到钟表的作用,系统可以设置和读取FH8563中存放的当前时间,从而对数据进行相应处理(例如计费、显示、记录等)。它内部集成了一个可编程的Alarm功能,在当前时间与Alarm设置时间一致,且对应的中断条件使能时,产生中断。

FH8563 内部集成了一个可编程时钟输出,一个中断输出,并集成了内部振荡器电容,最大限度减少了电路板上的布线数目,非常适合于复杂系统。所有的地址和数据都通过I2C总线接口串行传递,I2C总线的从地址为:0xA3(读数据)、0xA2(写数据)。最大总线速度为400Kbits/s,每次读写数据后,内嵌的字地址寄存器会自动递增,可以实现连续读写功能。

典型应用电路

芯片引脚功能

电气特性

● 宽工作电压:0.9V-5.5V

● 低休眠电流:0.4uA(3.3V下的典型值)

● I2C通信频率最高支持400KHz

● 具有世纪标志位,万年历日期2000年-2199年

● 可编程时钟输出32.768KHz、1024Hz、32Hz、1Hz

● 内部集成振荡器电容

● 内部集成定时器

● 内部集成报警功能

● 中断开漏输出功能

● 封装形式:SOP-8L、TSSOP-8L、MSOP-8L、DFN3*3-8L(新增)

极限参数

应用领域

● 电池电源产品

● 便携、手持设备

● 复费率电度表、IC卡水表、IC卡煤气表

● 移动电话和传真机

● 门禁系统

PCB 设计应用说明

下图为 FH8563 的应用图示。SCL和SDA两个引脚需要连接到控制器的I2C总线上,在该图中未画出I2C总线的上拉电阻,该上拉电阻通常取值4.7KΩ左右。电池BAT(图中标注CR1220)作为后备电源,当VDD低于电池电压时,由电池向芯片供电。芯片的OSCI引脚还可以接入可调电容用以微调时钟频率用。CLKOUT和INT,可以根据实际需要接入电路中。

石英晶振频率的调整

由于 FH8563 用来计时,计时的精确性取决于所接的石英晶振频率的准确度。微小的频率偏差日积月累后就会距标准时间越来越大。这里给出调整石英晶振频率的若干方法。

方法1:使用固定的OSCI电容。在应用电路板上经试验获得所需的电容平均值,然后采用该定值的电容元件。频率的测定,以通电后在CLKOUT引脚测出32.768KHz为最好。频率值偏差取决于石英晶片和电容的性能偏差,及其之间的偏差(平均为±5ppm)。经试验很容易将时间偏离控制在5分钟/年以内。

方法2:OSCI微调电容。通过调整OSCI引脚与地的微调电容,使加电时CLKOUT引脚输出准确的32.768KHz信号。

方法3:OSCI输出。直接测量OSCI引脚的输出,应考虑到测试时所引入的电容。

芯片时钟精度的校准

FH8563 走时精度是否准确取决于FH8563的晶体是否与负载电容匹配,推荐使用等效负载电容为12.5pF的晶体,OSCI端接15~21pF的负载电容,FH8563第7脚为CLKOUT,连接4.7KΩ上拉电阻,测试CLKOUT输出时钟频率,如果频率比32.768KHz快,则需要增大OSCI端电容,如果频率比32.768KHz慢,则减小OSCI端负载电容。

软件编程注意事项

当Timer功能打开并设置,Timer发生中断后,软件可以通过清除寄存器TF bit清除中断标志,并读取TF标志,确认清除正确。

芯片实物图